Garrett.

I love engineering.

A computer engineer with a passion for chips. I love low-level software and high-level hardware, especially whenever the two intersect.

A computer engineer with a passion for chips. I love low-level software and high-level hardware, especially whenever the two intersect.

Who I am:

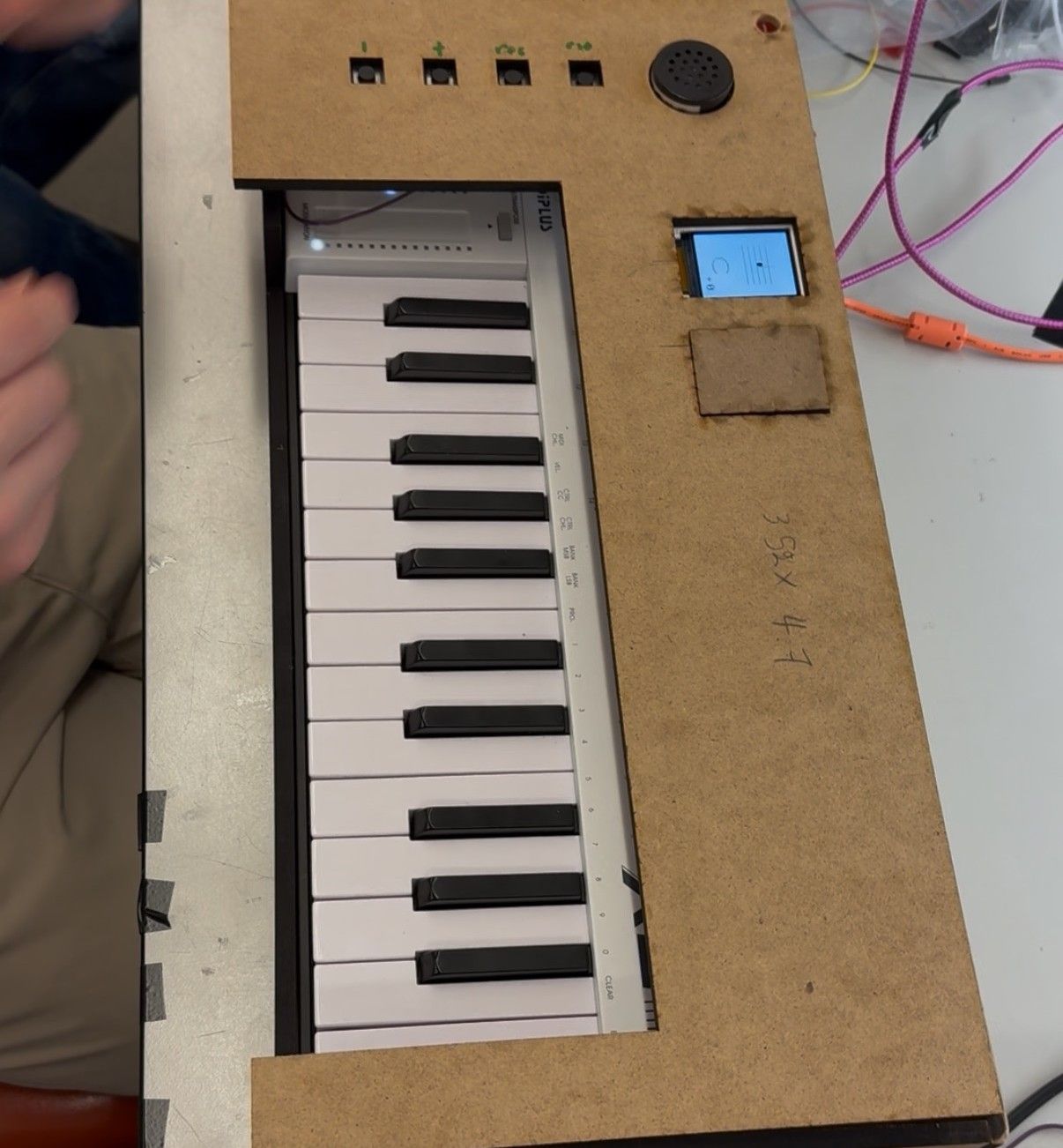

I was born and raised in Cincinnati, Ohio, a city I’m proud to call home even as I embrace opportunities to experience new places and cultures. My journey has been shaped by a passion for travel, sports, and music, each contributing to my curiosity, adaptability, and collaborative spirit. Whether navigating a new city, engaging with diverse teams, or playing music with friends, these experiences have deepened my ability to connect with people from all walks of life. These interests outside of engineering have broadened my perspective, encouraging creative problem-solving and a balanced approach to my professional work. I’m known for my enthusiasm, open communication, and willingness to jump into new challenges with energy and positivity. At the core, I believe in bringing authenticity and a sense of fun to every environment—qualities that, I’ve found, help build strong, effective teams and lasting professional relationships.

What I Do:

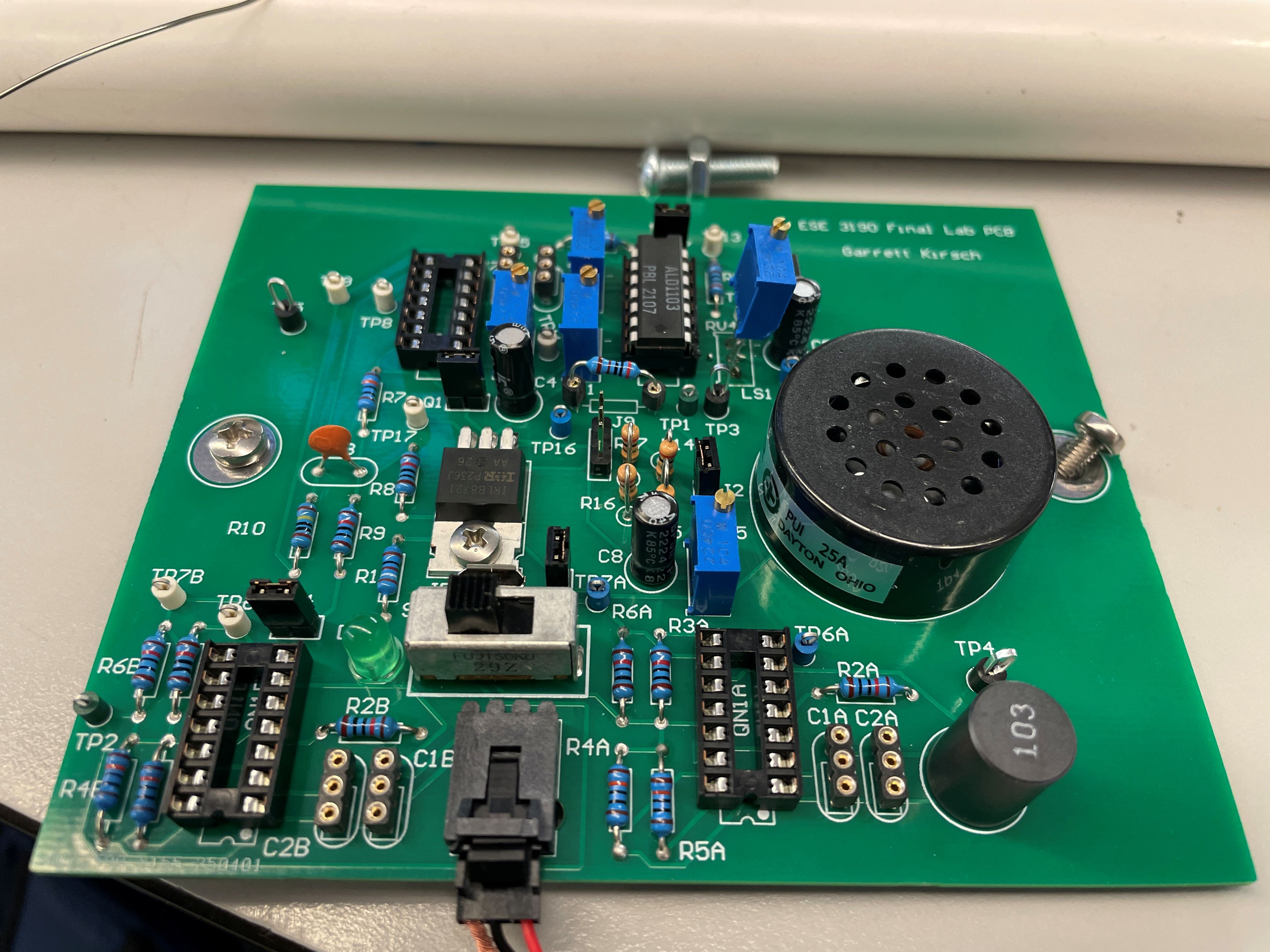

I am a computer engineering student at the University of Pennsylvania with a strong interest in chip design and computer systems. My academic background bridges both hardware and software, and I am particularly passionate about working at the intersection of these fields. Although my studies often involve late nights troubleshooting in the lab or analyzing waveforms, the experience of bringing innovative projects to life continually fuels my desire to push boundaries and contribute new ideas to the field.

I am currently working full-time in the CyberSavvy Lab under Professors Jinf Li and Andre DeHon, where I am responsible for turning our FPGAs into cloud resources using Docker and Kubernetes.

Tools and Programming Languages:Extracurriculars

Extracurriculars